# University of California, Santa Barbara

Department of Electrical and Computer Engineering

ECE 152A – Digital Design Principles

Homework #5

## Problem #1.

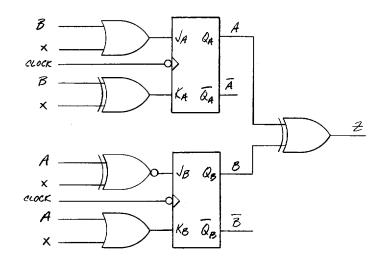

For the logic diagram below, complete the timing diagram. You can assume the gate delays are much shorter than the clock period.

Is this a Mealy machine or a Moore machine and why?

A=0\_\_\_\_

B=0\_\_\_\_

#### Problem #2.

For the network shown below:

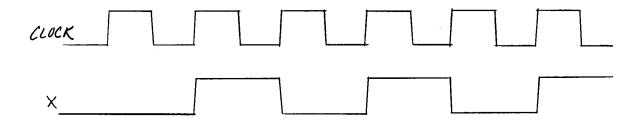

1. Construct a timing diagram for the input sequence:

Assume that:

- 1) X, A and B are all initially equal to 0

- 2) All transitions of the input X occur on the rising edge of the clock

- 3) gate delays are much shorter than the clock period.

Include all inputs (CLK, X) state variables (A, B) and outputs (Z) in your timing diagram.

- 2. Construct next state maps for the network.

- 3. Construct the state table for the network.

- 4. Construct the state diagram for the network

- 5. Redesign the network as a Moore machine. Include a state diagram, state table, next state maps and flip flop input maps. Implement your design with negative edge triggered JK flip flops.

- 6. For the Moore machine designed in part 5, construct a timing diagram for the input sequence:

X = 0 1 0 1 0 1 1 1 0

As in part 1, assume that:

- 1) X, A and B are all initially equal to 0

- 2) All transitions of the input X occur on the rising edge of the clock

- 3) gate delays are much shorter than the clock period.

Include all inputs (CLK, X) state variables (A, B) and outputs (Z) in your timing diagram.

## Problem #3.

A Mealy machine is defined by the following state table:

| PS | NS,z |      |

|----|------|------|

| AB | x=0  | x=1  |

| 00 | 01,0 | 10,1 |

| 01 | 01,1 | 11,1 |

| 10 | 01,1 | 00,0 |

| 11 | 10,0 | 00,0 |

- 1. Construct the state diagram for the Mealy machine.

- 2. Assuming that 00 is the initial state, determine the sequence of states and outputs in response to the input sequence:

$0 \rightarrow 0 \rightarrow 1 \rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 1$

- 3. Construct the state diagram for the equivalent Moore machine.

- 4. Construct a state table for the equivalent Moore machine.

- 5. Demonstrate that the machines are equivalent by applying the same input sequence as applied to the Mealy machine:

$$0 \rightarrow 0 \rightarrow 1 \rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 1$$

and observing the same output sequence. Identify both the sequence of states and the sequence of outputs (The state sequence will be different, but the output sequence should be the same).

# Problem #4.

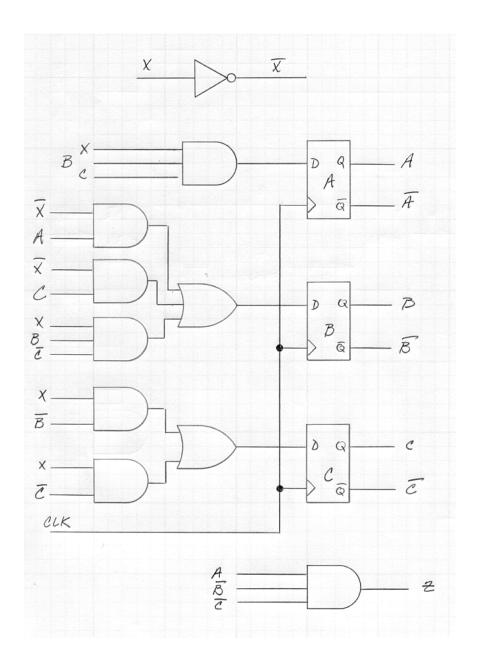

Consider the state machine below having a single input x, a single output z and three state variables, A, B and C:

- 1. Is this a Mealy machine or a Moore machine (and why)?

- 2. From the logic diagram, construct next state maps for the three state variables (A, B and C)

- 3. From the next state maps, construct a state table. Include both the next state and output information.

- 4. From the state table construct the state diagram. Include the output information on the state diagram as is appropriate for this type of machine.

- 5. This state machine implements a sequence detector. The output z goes high when the correct sequence has been detected. Based on the state diagram and assuming that 000 is the initial state, what is the "correct" input sequence?